Tuning For Better MemTweakIt Scores

If you're getting into MemTweakIt with your P67/Z68/Z77 ASUS motherboard, you will want to read up on how exactly the scores are calculated in order to get a better result. MemTweakIt is designed not as a hardcore competitive tweaking program, but rather the algorithms are setup for a more fun approach that promotes real tweaking efforts, rather than just buying or binning the fastest kit. A, B, C & D are principle factors in MemTweakIt's scoring, and each has relative weighting. It's also worth noting the code does not treat Sandy Bridge, Ivy Bridge or Sandy Bridge-E CPUs equally, due to architecture differences.

Intel 'Ivy Bridge' 3rd Generation Core Processors on LGA1155

DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iTRWDRDD + _pTSet->m_iTWRDRDD + _pTSet->m_iTRWSR); Overall the calculation is as follows: _pTSet->m_fEfficiency = (A * 127500.0f) / (53.0f * B + 0.6f * C + 20.0f * D); Then, finally, if you run in dual chanel with an Ivy Bridge CPU, the score will be multiplied by 1.92x compared to single channel. if (_pTSet->m_iNbChannels == 2) _pTSet->m_fEfficiency *= 1.92f;

DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iTRWDRDD + _pTSet->m_iTWRDRDD + _pTSet->m_iTRWSR); Overall the calculation is as follows: _pTSet->m_fEfficiency = (A * 127500.0f) / (53.0f * B + 0.6f * C + 20.0f * D); Then, finally, if you run in dual chanel with an Ivy Bridge CPU, the score will be multiplied by 1.92x compared to single channel. if (_pTSet->m_iNbChannels == 2) _pTSet->m_fEfficiency *= 1.92f;

Intel 'Sandy Bridge' 2nd Generation Core Processors on LGA1155

DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iTRWDRDD + _pTSet->m_iTWRDRDD + _pTSet->m_iTRWSR); Overall the calculation is as follows: _pTSet->m_fEfficiency = (A * 127500.0f) / (53.0f * B + 0.6f * C + 20.0f * D); Then, finally, if you run in dual chanel with an Sandy Bridge CPU, the score will be multiplied by 1.8x compared to single channel. if (_pTSet->m_iNbChannels == 2) _pTSet->m_fEfficiency *= 1.8f;

DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iTRWDRDD + _pTSet->m_iTWRDRDD + _pTSet->m_iTRWSR); Overall the calculation is as follows: _pTSet->m_fEfficiency = (A * 127500.0f) / (53.0f * B + 0.6f * C + 20.0f * D); Then, finally, if you run in dual chanel with an Sandy Bridge CPU, the score will be multiplied by 1.8x compared to single channel. if (_pTSet->m_iNbChannels == 2) _pTSet->m_fEfficiency *= 1.8f;

Intel 'Sandy-Bridge-E' 3rd Generation Core-i7 Processors on LGA2011

Due to the fact LGA2011 is quad-channel, not dual-channel, an additional Z-factor for total DRAM size is added while channel count is removed. The rest is largely the same. As before, DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (float)(_pTSet->m_iT_CCD) + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iT_WRDR + _pTSet->m_iT_WRDD + _pTSet->m_iTRWSR); float Z = (float)dsize; Overall the calculation is as follows: _pTSet->m_fEfficiency = 2.1f * ((A * 127500.0f) + (Z * 1000.0f)) / (53.0f * B + 0.6f * C + 20.0f * D);

Due to the fact LGA2011 is quad-channel, not dual-channel, an additional Z-factor for total DRAM size is added while channel count is removed. The rest is largely the same. As before, DRAM frequency has a high weighting, while A looks at the the baseclock is multiplied by the ratio used: float A = _pTSet->m_fBCLK * _pTSet->m_fRatio; Set B checks the primary timings (CR = Command Rate). float B = _pTSet->m_fCL + (float)_pTSet->m_itRCD + (float)_pTSet->m_itRP + (float)(_pTSet->m_iT_CCD) + (9.0f * (float)_pTSet->m_iCR); C & D check the secondary and tertiary timings, and has the lowest weighting; float C = (float)(_pTSet->m_itRAS + _pTSet->m_itRRD + _pTSet->m_iREFCycleTime + _pTSet->m_iRefreshInterval + _pTSet->m_itWTR + _pTSet->m_itRTP + _pTSet->m_itCKE + _pTSet->m_itFAW + _pTSet->m_itWR + _pTSet->m_itWCL); float D = (float)(_pTSet->m_iTRRDR + _pTSet->m_iTRRDD + _pTSet->m_iTWWDR + _pTSet->m_iTWWDD + _pTSet->m_iT_WRDR + _pTSet->m_iT_WRDD + _pTSet->m_iTRWSR); float Z = (float)dsize; Overall the calculation is as follows: _pTSet->m_fEfficiency = 2.1f * ((A * 127500.0f) + (Z * 1000.0f)) / (53.0f * B + 0.6f * C + 20.0f * D);

Author

Popular Posts

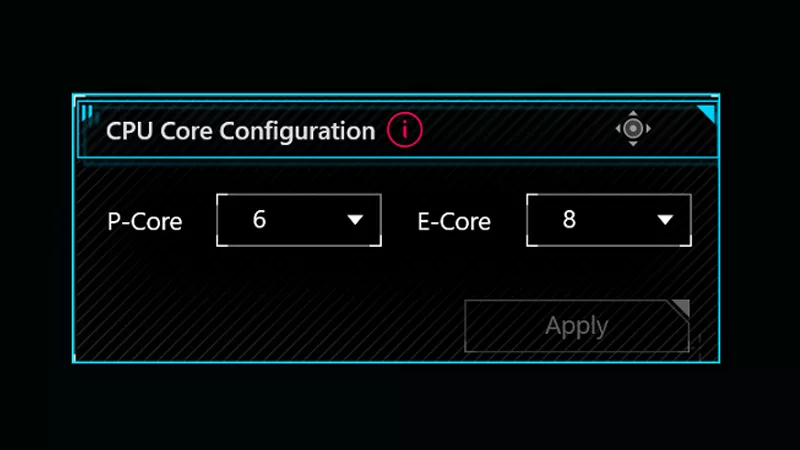

How to adjust your laptop's P-Cores and E-Cores for better performance and battery life

Introducing the ROG Astral GeForce RTX 5090 and 5080: a new frontier of gaming graphics

How to Cleanly Uninstall and Reinstall Armoury Crate

How to configure your PC's RGB lighting with Aura Sync

How to upgrade the SSD and reinstall Windows on your ROG Ally or Ally X

LATEST ARTICLES

See the mammoth ROG Dominus build that takes Intel's 28-core Xeon W-3175X to the Extreme

The ROG Dominus Extreme pushes the boundaries of PC performance in our awesome CES 2019 build.

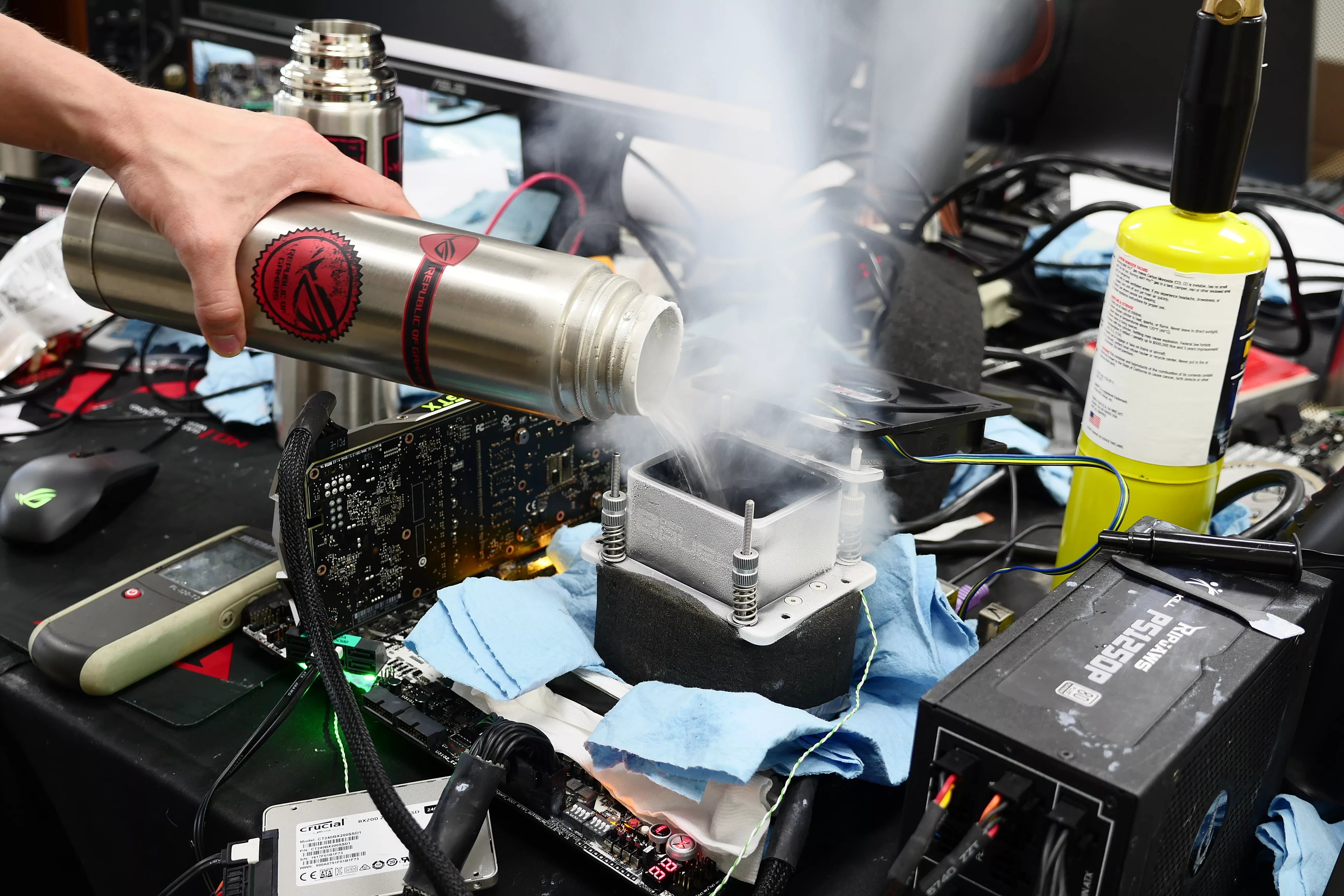

Breaking world records with the ROG Maximus XI Gene and the Intel Core i9-9900K

Tasked with pushing performance on the Z390 platform as far as possible, we invited the best overclockers to ROG HQ for a week of extreme overclocking.

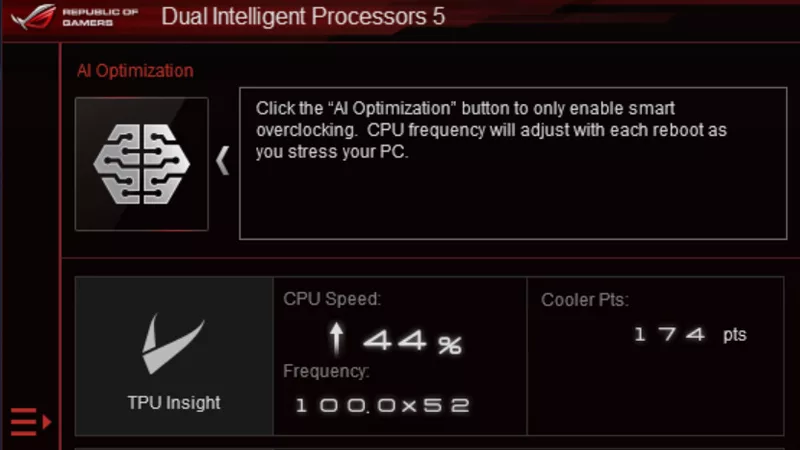

How to overclock your system using AI Overclocking

AI Overclocking one-click tuning makes its debut on Z390 motherboards and we have a quick how-to guide to get you started.

HW GURUS win the ROG OC Showdown Team Edition 2

The results are in from our second ROG OC Showdown Team Edition. See who posted the top scores.

Breaking records with the Maximus X Apex and i7-8700K

ROG is obsessed with chasing the highest overclocks and fastest performance, and Coffee Lake is our new muse on the Maximus X Apex.

The Rampage VI Apex claims more performance victories with Intel's new Core i9-7940X and i9-7980XE

After dominating extreme overclocking with the first wave of Skylake-X CPUs, we've taken the latest 14- and 18-core models to sub-zero extremes.